CPLD 무조건 따라하기

0. 준비물

- http://cgi.chol.com/~kohyc/armcpld/index.cgi에서 판매하는 S3C44B0X+CPLD보드

1. Software 다운로드

먼저 http://www.xilinx.com/webpack/index.htm에서 ISE WebPACK 7.1i를 다운로드 받는다.

다운로드하기 전에 xilinx에 먼저 등록해야 한다. 등록은 무료이고 등록절차는 각자 알아서 해결한다.

그리고 위의 페이지에 나와있는 내용을 주의 깊게 읽어보고 자신의 PC시스템과 맞는지 확인하고, 필요한 사항은 Upgrade(Windows XP나 2000은 Service Pack을 적용한다)한다.

다운로드 파일은 Web Install일 경우에 약 5Mbyte, Complete Software일 경우에 약 372Mbyte이다. 가능하면 Complete Software를 다운로드 받아 인스톨 하도록 하자.

이 교재에서는 Complete Software를 다운로드 한후 인스톨 한다.

WebPack을 인스톨 하였으면, xilinx의 홈페이지에서 ISE WebPACK 서비스팩을 잘 찾아서다운로드한 후 인스톨 한다.

현재는 웹팩 서비스팩 1이 최신 버전이다. (약 310Mbyte)

그리고 ftp://ftp.xilinx.com/pub/swhelp/cpld/sr21168.zip를 다운로드 받아 패치한다.

WebPack + Service Pack1 에는 CPLD(XC9500계열 칩)에 버그가 있어서 위의 압축화일을 반드시 다운로드 받아 파일을 업데이트 시켜야 한다. 이 버그는 Web Service Pack2에서 고쳐질 예정이라고 한다.

모델심이 필요한 사용자는 MXE_III Starter도 다운로드 받아 인스톨 한다.

이 교재에서는 모델심은 취급하지 않는다.

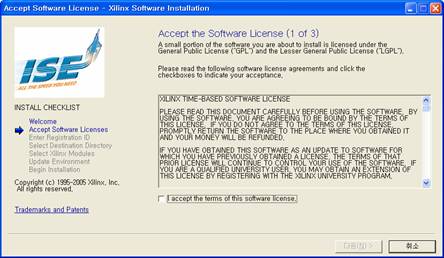

2. 설치

WebPACK_71_fcfull_i.exe의 다운로드가 끝나면 실행한다.

압축화일이 풀리는데 한참 시간이 걸린후에 다음과 같은 시작화면이 나온다.

라이센스 Accept란을 check하고 다음으로 계속 넘어간다.

설피프로그램이 설치도중 이전버전을 발견하면 uninstall시킬지를 물어본다. 잘 생각해서 언인스톨 시킨다. Begin Installation을 시작하면 아주 한참동안 설치를 한다.

인스톨이 모두 끝나면 최신 Update내용이 있는지 xilinx site에서 확인하겠다는 창이 뜬다.

홈페이지를 보면 7.1의 update인 7.1.01i가 2005년 3월 17일에 발표되었다.

이 update역시 다운받은 후에 설치한다.

그리고 sr21168.zip의 내용도 replace한다.

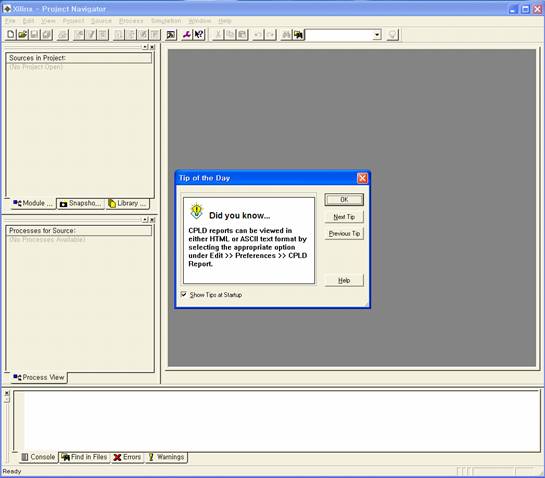

3. 실행

실행은 바탕화면에 있는 Xilinx ISE 7.1i 아이콘을 더블 클릭하거나, 시작-모든프로그램-Xilinx ISE 7.1i-Project Navigator선택하여 실행한다.

실행하면 다음과 같은 화면이 나온다.

Tip of the day의 내용은 매번 실행할때마다 바뀐다.

4. 예제 – AND/OR gate

이제 BW-CPLD보드에서 테스트해 볼 수 있는 간단한 예제를 만들어 보자.

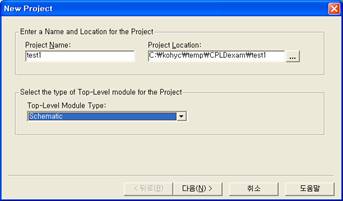

메뉴의 File-New Project를 클릭한다.

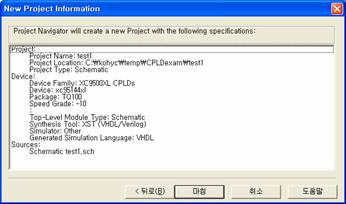

적당한 Project Location을 먼저 지정하고, Project Name을 지정하면 Name 폴더가 Location에 추가된다. Top-Level Module Type은 Schematic을 지정하고 ‘다음’을 클릭한다.

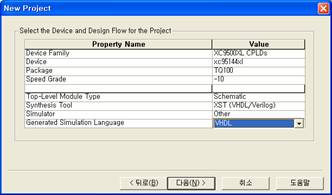

이 화면에서 사용하려는 CPLD나 FPGA를 지정한다. Device Family, Device, Package, Speed Grade는 BW-CPLD보드에 부착된 CPLD를 지정한다.

Top-Level Module Type, Synthesis Tool, Simulator, Generated Simulation Language는 위의 화면과 동일하게 지정한다. 그리고 ‘다음’을 클릭한다.

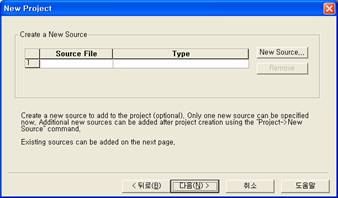

이 화면에서 ‘New Source’를 클릭한다. 그러면 다음과 같은 화면이 나타난다.

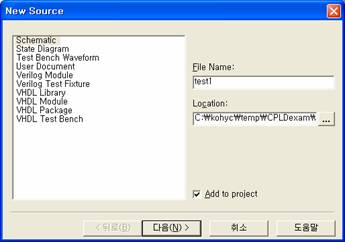

이 화면에서 ‘Schematic’을 먼저 선택한후 File Name에 ‘test1’이라고 입력한다.

그리고 다음을 클릭한다.

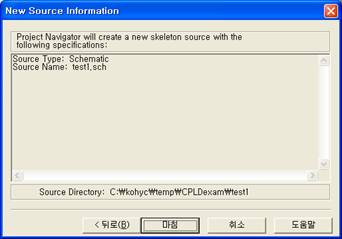

그러면 위와 같이 자동으로 sch확장자가 추가된뒤 프로젝트에 추가된다.

여기서 ‘마침’을 클릭한다.

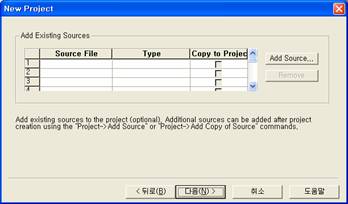

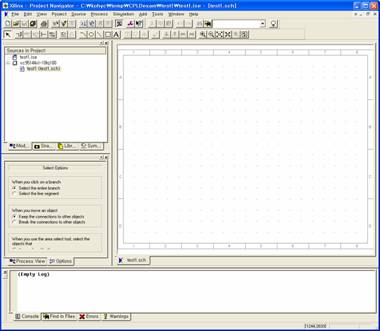

그러면 다음과 같은 화면이 나온다.

여기서 ‘다음’을 클릭한다.

위화면에서는 추가할 소스가 없음으로 그냥 ‘다음’을 클릭한다.

그러면 위와 같이 새로이 생성될 프로젝트에 대한 설명이 나온다.

여기서 마침을 선택한다. 그러면 프로젝트 생성이 끝났다.

이 화면의 Source in Projcet창에서 이 프로젝트의 정보를 볼수 있다.

이쯤에서 메뉴-File-Save all을 클릭한다. 그러면 프로젝트의 모든 파일이 저장된다.

다음에 이 프로젝트를 Open하려면 프로젝트 폴더에 있는 test1.ise를 File-Open projcet에서 Open하면 된다.

이제 원하는 회로를 test1.sch영역에 그리면 된다.

이제 간단한 AND GATE와 OR GATE를 그려 보자.

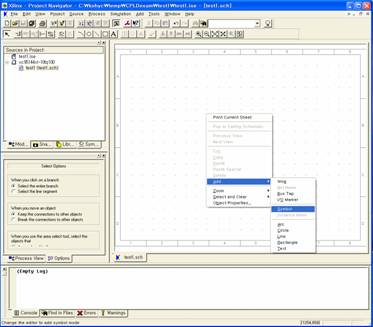

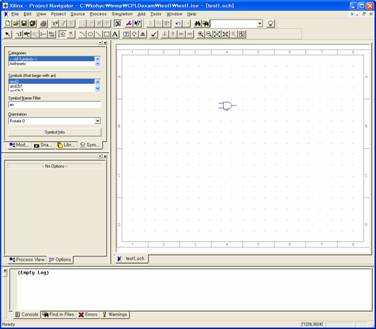

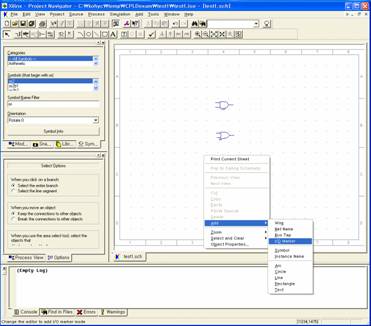

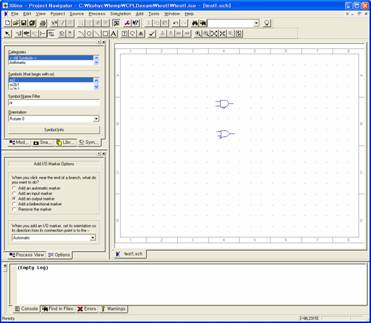

test1.sch영역에서 오른쪽 마우스버튼을 클릭하면 위 화면과 같이 메뉴가 나온다. 이 메뉴에서 Add-Symbol을 선택하면 다음과 같이 화면이 바뀐다.

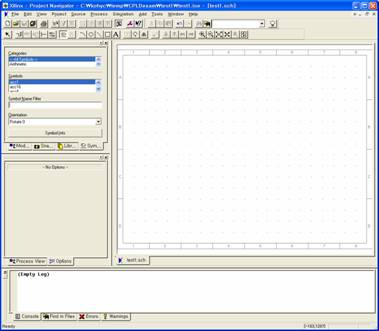

화면의 왼쪽 윗부분이 Symbol 메뉴로 바뀌었다. 여기서 Symbol Name Filter영역에 ‘an’두글자만 입력한다.

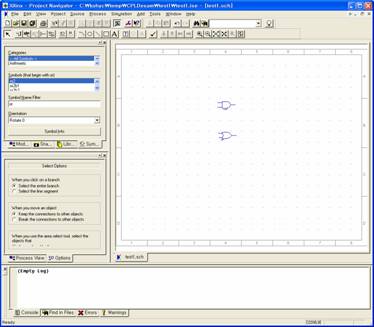

그리면 위와 같이 an으로 시작하는 심볼이 나온다. 여기서 and2를 선택하고 마우스를 test1.sch영역으로 옮겨서 중앙 부분에 클릭하여 위치시킨다.

마찬가지로 Or gate도 위치시킨다.

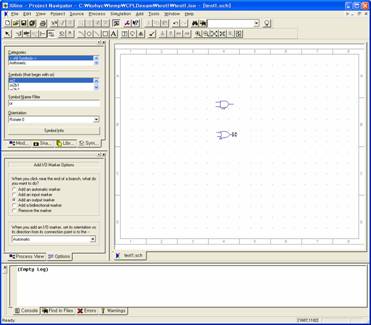

이제 I/O Tab를 위치시키자.

마우스 오른쪽을 클릭하여 ADD-I/O Marker를 선택한다.

그러면 위와 같이 왼쪽 중간에 Add I/O Marker Options이 생긴다. 여기서 Add an Output marker를 선택한다.

그리고 마우스 커서를 Or gate의 출력단에 위치시키면 위와 같은 위치가능 표시(4개의 점)가 나온다. 이때 마우스를 클릭하여 Output Marker를 위치시킨다.

마찬가지로 And gate의 출력단에도 Output Marker를 위치시킨다.

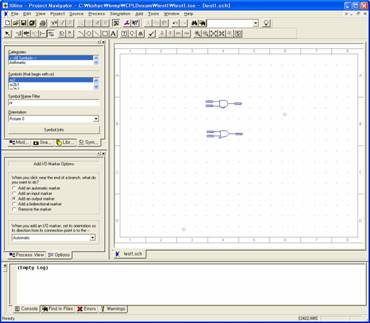

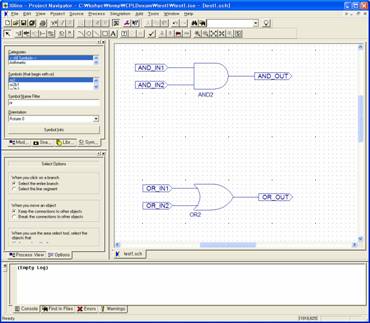

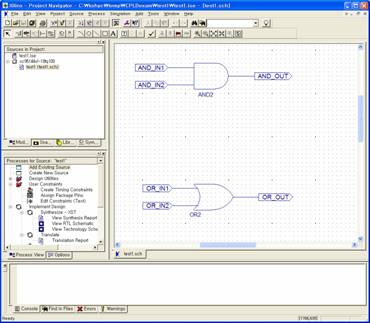

그리고 Optons에서 input marker를 지정한후 AND gate/Or gate의 각 입력핀에 위치시킨다. 그러면 완성된 그림은 다음과 같다.

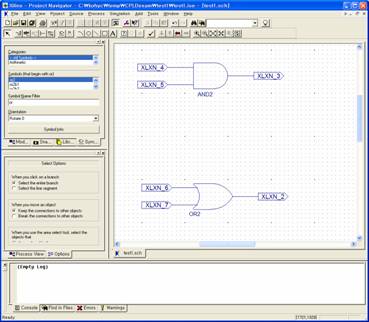

이 화면을 확대하면 다음과 같다.

입출력 핀에 Schematic Editor가 임의로 Net Name을 할당했다.

이 Net Name을 수정해보자.

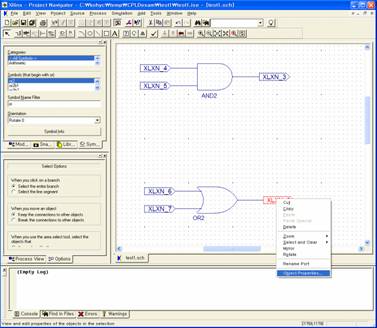

XLXN_2에 마우스를 위치시킨후 오른쪽 마우스 버튼을 클릭하면 다음과 같은 화면이 된다.

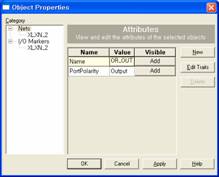

여기서 object properties를 선택하면 다음창이 나온다.

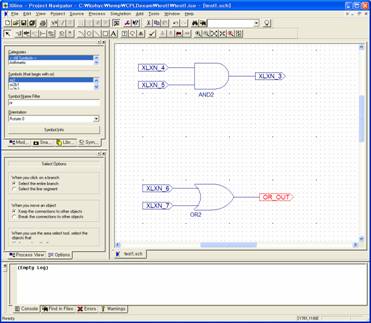

여기서 Name난에 OR_OUT라고 입력한후 OK를 누르면 Net Name이 수정된다.

이와 같은 방법으로 모든 Net Name을 다음 그림과 같이 수정하자.

이제 이 test1.sch를 저장하자. 저장은 File메뉴 아래에 있는 디스크 아이콘을 클릭하거나,

File-Save를 선택하면 된다.

이제 왼쪽 상단의 Mod..(심볼정보가 있는 곳의 가장 왼쪽 탭)을 클릭하고, Module 창의test1(test1.sch)을 클릭하고, Process View를 클릭한다.

그러면 위와 같은 화면이 나온다.

여기서 마우스를 Process View의 Implement Design에 위치시키고 더블클릭을 한다.

그러면 test1.sch상의 회로가 합성된다. 진행사항은 화면아래의 Console창에 나타나며,

화면의 가장 아래쪽/오른쪽에 진행상태가 간략하게 표시된다.

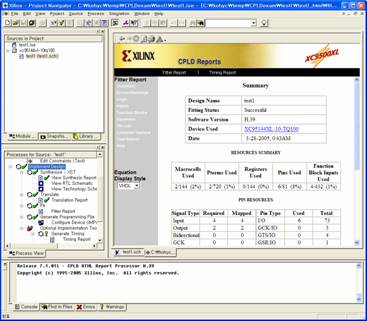

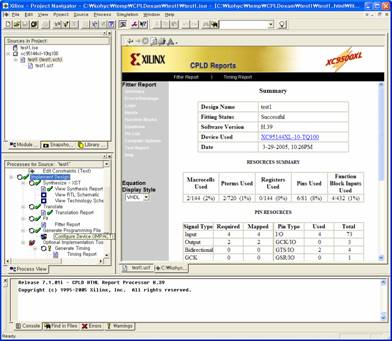

위 화면은 합성이 끝난 화면으로 에러 없이 정상적으로 회로 합성이 진행되면, Process View에 각 Process항목에 초록색 체크 표시가 나오며, 합성이 완료되면 화면 중앙에 CPLD report가 나온다. 이 리포트는 이 프로젝트 합성과 관련된 각종정보가 나온다.

Process View에 특정 항목에 빨간색 X표시가 나오면 해당 절차에서 에러가 발생했다는 뜻이다. 회로 합성중 에러가 발생하면 다음절차로 진행하지 않고 막바로 정지한 후에 Console창에 에러 내용을 표시한다.

이제 이 프로젝트 폴더를 탐색기 등으로 보면 test1.jed라는 파일이 생성되어 있다.

이 test1.jed라는 file을 CPLD에 write하면 CPLD는 test1.sch의 회로대로 동작을 한다.

여기서 잠깐만..

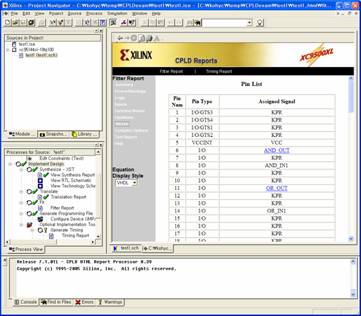

위 예제에서 6개의 Net를 사용했지만 해당 Net가 CPLD의 어느핀에 연결되는지는 정의하지 않았다. 어떤 NET가 CPLD의 어느 핀으로 할당되었는지 확인하려면 Fitter Report(화면 오른쪽의 Report 화면의 Pin list를 클릭하면 된다.

위의 report를 보면 AND_OUT은 CPLD의 6번핀에, OR_OUT은 CPLD의 11번핀, AND_IN1은 8번핀, AND_IN2은 92번핀, OR_IN1은 14번핀, OR_IN2는 71번핀에 할당되었다. (혹은 사용자의 시스템에 따라 핀 번호는 바뀔수 있다.)

핀을 지정하지 않고 합성하면 합성중에 ISE프로그램이 임의로 핀과 네트를 연결해 버린다.

위의 회로들 BW_CPLD보드에서 테스트 하려면, BW_CPLD보드의 I/O Test보드에 핀에 맞게 수정해야 한다. BW_CPLD보드는 8개의 SW입력과 8개의 LED출력 보드를 연결할 수 있다. 이 SW와 LED를 위 회로의 입출력 단자와 연결하면 위 회로를 테스트 할 수 있다.

따라서 입력핀과 출력핀을 BW_CPLD보드의 회로에 맞게 지정해야 한다.

BW_CPLD보드의 회로도(bw_board_CPLD.pdf)를 확인해보면 IO1~IO16중에서 홀수번호가 SW입력, 짝수번호가 LED출력 Net이다.

이중에서 IO1,IO3,IO5,IO7을 AND_IN1,AND_IN2,OR_IN1,OR_IN2에 차례로 할당하고, IO2를 AND_OUT에 IO4를 OR_OUT에 할당해 보자.

보드의 회로도를 잘 검토해보면 AND_IN1은 CPLD 3번핀, AND_IN2는 6번핀, OR_IN1은 9번핀, OR_IN2는 94번핀, AND_OUT은 4번핀, OR_OUT은 8번핀이 된다.

이 핀 내용을 User Constraints 형태로 ISE에 알려주면 된다.

이제 이 user constraints를 만드는 방법을 알아보자.

먼저 Process View의 Optional Implementation tools트리에 있는 Lock Pins를 더블클릭한다. 그러면 test1_locked.ucf라는 파일이 생성되었다는 메시지가 console창에 나온다.

이 파일을 text editor나 Project Navigator에서 open해 보면 다음 내용이 나온다.

#PINLOCK_BEGIN #Mon Mar 28 01:15:24 2005

NET "AND_IN1" LOC = "S:PIN8";NET "AND_IN2" LOC = "S:PIN92";NET "OR_IN1" LOC = "S:PIN14";NET "OR_IN2" LOC = "S:PIN71";NET "AND_OUT" LOC = "S:PIN6";NET "OR_OUT" LOC = "S:PIN11";#PINLOCK_END

이 내용이 Net가 CPLD의 핀에 할당된 것을 나타낸다.

이 파일을 BW_Board CPLD –SW/LED보드의 회로에 맞게 다음과 같이 수정한뒤 test1.ucf로 저장한다. 수정은 text editor로 하면 된다.

#PINLOCK_BEGIN #Mon Mar 28 01:15:24 2005

NET "AND_IN1" LOC = "S:PIN3";NET "AND_IN2" LOC = "S:PIN6";NET "OR_IN1" LOC = "S:PIN9";NET "OR_IN2" LOC = "S:PIN94";NET "AND_OUT" LOC = "S:PIN4";NET "OR_OUT" LOC = "S:PIN8";#PINLOCK_END

test1_locked.ucf이라는 파일이름은 사용자가 별도의 ucf파일을 지정하지 않았을 때 나타나는 이름이다. 사용자가 test1.ucf라는 이름으로 Module에 추가하면, 이후에 Optional Implementation tools-Lock Pins을 실행하면 사용자가 지정한 이름으로 생성된다.

이렇게 저장한 파일을 user constraint로 소스에 추가한다.

추가 방법은 다음과 같다.

Sources in project에서 test1(test1.sch)를 마우스 커서로 클릭한후 오른쪽 마우스 버튼을 누른후에 Add Source를 선택한다. 그러면 Add existing source창이 생기는데, 여기서 조금전에 저장한 test1.ucf를 지정한다.

그러면 test1의 하위에 test1.ucf가 추가된다.

이제 마우스 커서로 Source In Project 영역의 test1(test1.sch)를 클릭하여 선택하고, Process View의 Implementation Design을 지정한후 오른쪽 마우스 버튼을 누르고 Rerun All을 선택한다. 그러면 이 프로젝트는 처음부터 다시 합성된다.

Implementation Design의 아래에 있는 트리가 모두 초록색 체크표시가 되고 나서 합성이 끝난다. 에러없이 합성이 완성되었으면, Fitter Report의 Pin List를 확인하자.

Report상의 Pin List와 BW_Board_CPLD회로도의 IN(SW) net와 OUT(LED) net가 일치하면 test1.sch는 우리가 원하는 대로 합성되었다.

이제 이렇게 해서 합성된 결과물이 프로젝트 폴더에 test1.jed파일이라는 이름으로 생겨난다. 이 test1.jed(bit stream file)을 CPLD에 Write하기만 하면 CPLD는 test1.sch의 내용대로 동작할 것이다.

이제 jed파일을 CPLD에 write하는 방법을 알아보자.

5. CPLD에 Write하기.

이제 BW CPLD보드와 SW/LED보드, JTAG Cable을 준비한다.

보드에 SW/LED보드를 부착하고, JTAG CABLE도 CPLD의 JTAG 커넥터에 연결한다. JTAG CABLE은 25핀 확장 케이블을 이용하여 PC의 프린터 포트에 연결한다. JTAG의 6핀커넥터를 Board에 연결할때는 방향이 바뀌지 않도록 주의한다.(빨간선이 1번핀에 연결되어야 한다. 사진참조)

JTAG CABLE연결 사진

보드에 전원을 연결하고 전원스위치를 켠다.

이 상태에서 ISE의 Process View의 Implement Design-Generate Programming File-Configure Device를 더블클릭한다.

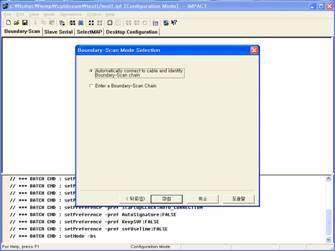

그러면 iMPACT라는 JTAG Configuration 프로그램이 실행된다. Process View의 Configure Device를 더블클릭하거나, 윈도우 시작-모든프로그램-Xilinx ISE 7.1i-Accessories – iMPACT를 클릭해도 된다.

이 화면에서 Automatically Connect to Cable~~를 선택하고 ‘마침’을 클릭한다.

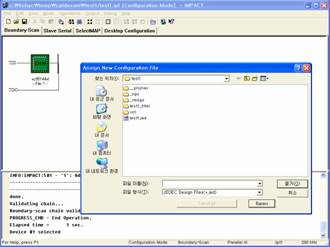

보드에 전원이 켜져있고 JTAG의 연결이 정상이면 다음과 같은 메시지가 나온다.

이 메시지는 CPLD device 1개가 JTAG Cable에 연결되어 있다는 뜻이다.

확인을 클릭하면 다음과 같은 파일 Open창이 뜬다.

여기서 test1.jed파일을 지정한다.

그러면 다음 화면이 된다.

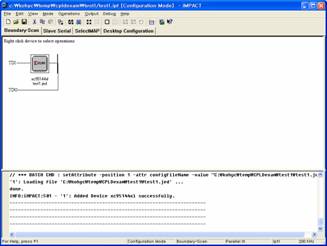

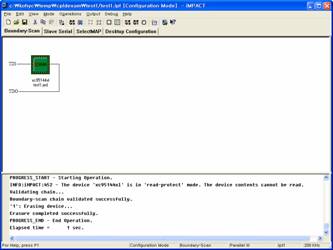

이제 마우스로 xc95144xl을 한번 클릭하여 선택되게 한다.

이제 마우스의 오른쪽 버튼을 클릭하여 erase를 선택하거나 메뉴의 Operation-erase를 선택한다.

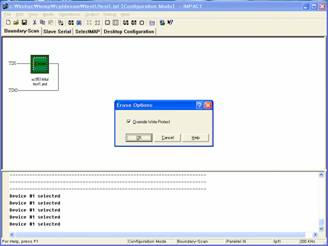

CPLD를 지우면서 Write Protect까지 같이 지울것인지 물어본다. 여기서 OK를 선택한다.

(CPLD에 Write Protect를 걸어서 Write한적이 있다면 이 erase메뉴에서 write protect를 지워야 한다. Write Protect를 한적이 없다면 이 Erase기능을 실행할 필요는 없다.)

OK를 누르면 아주 잠깐동안 진행 창이 나타났다 사라지고 화면 아래쪽에 Erase가 성공했다는 메시지가 나온다.

이제 test1.jed파일을 CPLD에 Write한다.

메뉴의 Operation-Program을 선택하거나 CPLD를 선택하고 오른쪽 마우스를 클릭하면 프로그램 메뉴가 나온다.

CPLD에 처음 write하는 경우라면 erase가 필요없다. 하지만 CPLD에 한번이라도 write한적이 있다면 erase를 먼저 해야 한다.

CPLD에는 Read Protect와 Write Protect를 걸수 있다.

Read Protect는 CPLD를 읽어서 jed file로 저장하는 것을 방지하는 기능이다.

Read Protect가 걸려있는 CPLD는 Bit Stream파일의 복사가 불가능 하지만, Protect가 걸려있지 않은 CPLD는 복사가 가능하다.

Write Protect는 CPLD에 Write하는 것을 방지하는 기능이다. 이 Write Protect를 풀려면 방금전의 Erase메뉴를 통해서 없앨 수 있다.

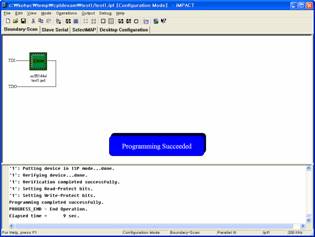

여기서 OK를 클릭하면 test1.jed의 내용이 CPLD에 Write된다.

진행상태창이 잠깐 나오고 다음과 같이 Programming이 성공했다는 메시지가 나온다.

이제 CPLD에 Write는 끝났다.

AND gate와 OR gate가 정상으로 동작하는지 확인해보자.